一、 问题的根源:为何DDR3如此“娇气”?吉林炒股配资平台

在数百MHz甚至更高频率下,DDR3总线上的任何微小瑕疵都会被急剧放大。主要挑战来自:

飞行时间差异:

DDR3的时钟(CK)、数据(DQ)和数据选通(DQS)信号在PCB走线上的长度不可能完全一致。长度的差异导致信号到达DDR3颗粒/FPGA的时间不同,即飞行时间 不同。这使得在控制器端发出的DQS边缘,无法精确对齐在DDR3颗粒端DQ数据的中心。

时钟偏移:

即使走线等长,由于FPGA内部和DDR3芯片内部的缓冲器差异,也会导致CK、DQS和DQ信号之间产生微小的时序偏移。

电压与温度变化:

系统运行中,PVT(工艺、电压、温度)的变化会动态地改变信号的传输延迟和建立/保持时间。

结论: 一个固定的、出厂即用的采样时序是无法应对这些动态变化的。因此,必须有一个在上电后、运行前的自动测量与调整过程,这就是 Training 。

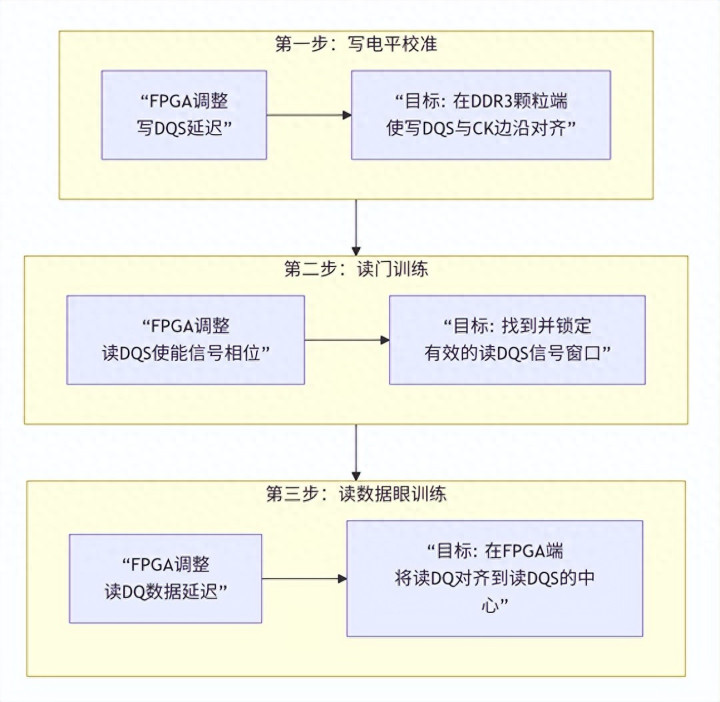

二、 Training Process 详解:三步曲

MIG的校准过程主要包含三个阶段,它们像一场精密的仪式,环环相扣。

阶段一:写电平校准 - 解决“写”操作的时序问题

目标: 确保在 DDR3颗粒的引脚上 ,写数据选通(DQS)的边沿能够精确对齐 写时钟(CK)的边沿 。

问题场景:

由于CK和DQS走线延迟不同,当FPGA同时发出CK和DQS时,它们到达DDR3颗粒时可能已经错位。DDR3颗粒是利用CK来锁存命令和地址的,而利用DQS来锁存写数据的。如果DQS相对于CK延迟太多,颗粒可能在正确的数据到来之前就去锁存,导致写入错误。

解决方案:MIG控制器让DDR3颗粒进入 写电平模式 。控制器发送一个特殊的 写电平调整模式命令 。DDR3颗粒会在其DQS引脚上 输出一个特定的模式 (通常是CK的复制品)。MIG控制器在FPGA端 监测返回的DQS信号 ,并 动态调整DQS的相位 ,直到在FPGA端捕获到的DQS边沿与内部的CK参考边沿对齐。这个调整量,就补偿了CK和DQS从FPGA到DDR3颗粒的飞行时间差。

简单比喻: 教练(FPGA)根据运动员(DDR3)返回的脚步声(DQS),调整自己喊口令(发出DQS)的时机,确保口令和运动员的起跑动作在跑道上(DDR3引脚处)同时发生。

阶段二:读门训练 - 找到“读”数据的开门时机

目标: 确定在读操作期间,应该在什么时候“开门”接收DQS信号。

问题场景:

在读操作中,DDR3颗粒会同时输出DQ数据和DQS选通信号。DQS在读取时是边沿对齐的(即在数据变化的边沿触发)。FPGA需要利用这个DQS来在数据的中心点进行采样。但是,DQS信号并不是持续存在的,它只在突发读传输期间有效。FPGA需要一个读使能信号来控制何时接收DQS。

解决方案:MIG控制器向DDR3写入一个已知的数据模式(如交替的0和1)。控制器发起读操作,并 扫描读DQS使能信号的相位 。控制器寻找一个 稳定的时间窗口 ,在这个窗口内,使能信号能可靠地捕获到有效的DQS脉冲,而不会捕获到DQS处于高阻态时的噪声。一旦找到这个最佳使能位置,就将其固定下来。

简单比喻: 教练需要找到精确的时机打开计时器的门,以确保只记录运动员的有效成绩,而不会记录他热身或休息时的无关动作。

阶段三:读数据眼训练 - 定位数据的最佳采样点

目标: 找到读DQS与读DQ之间的 最佳相位关系 ,确保FPGA在DQ数据的“眼图”中心进行采样,以获得最大的时序裕量。

问题场景:

即使DQS被正确使能,由于DQ和DQS信号在PCB和芯片内部的延迟差异,它们到达FPGA时也可能不是理想的边沿对齐关系。如果FPGA直接在DQS的上升沿采样DQ,可能会落在数据变化的边缘(建立/保持时间违例),导致采样错误。

解决方案:

这是最核心、最精细的一步。MIG控制器再次向DDR3写入一个已知的、复杂的测试模式(例如, walking 1‘s/0’s)。控制器发起连续的读操作。在FPGA端,MIG内部的延迟链开始工作。它会 系统地、微小地调整DQ相对于DQS的延迟 (或反之)。对于每一个延迟设置,控制器都检查读回的数据是否与预期模式匹配。通过扫描整个时钟周期,控制器可以绘制出一个 “数据眼图” 。这个眼图的中心,就是 误码率最低、时序裕量最大的最佳采样点 。控制器最终将延迟锁定在这个最佳点上。

简单比喻: 教练用高速摄像机(延迟链扫描)分析运动员冲线时(数据有效时)的每一帧画面,找到躯干最接近终点线的那个绝对最佳瞬间,并以此作为按下秒表的精确时刻。

三、 调试实战:当训练失败时我们该怎么办?

当你在Vivado中看到 init_calib_complete 为低,或者在ILA中看到持续的数据错误时,意味着训练失败了。以下是你应该遵循的排查思路:

1. 硬件第一性原理

训练失败,90%的原因在硬件。

电源: 用示波器检查DDR3的VDD、VTT、VREF电源是否稳定?纹波是否在规格之内? VREF尤其关键 ,它的不准会直接改变信号的判决门限。

时钟: 参考时钟和系统时钟的幅度、频率、抖动是否达标?

PCB检查:等长: 严格检查DQ/DQS组内等长、地址/命令/控制线与时钟的等长。违反等长规则是训练失败的常见原因。拓扑: 是否使用了正确的拓扑结构(如Fly-by)?端接电阻(ODT)的布局是否合理?SI: 是否有明显的阻抗不连续、串扰或反射?

2. 利用Vivado调试工具

Vivado提供了强大的工具来诊断训练问题。

查看校准报告:

在Implementation后的 DRC 和 Report 中,可以找到MIG的校准报告。它会详细列出每个训练阶段的状态(Pass/Fail),并给出可能的原因。

使用DDR Debug Toolkit(需要License):

这是终极武器。写眼图扫描: 它可以扫描并可视化写操作的时序裕量,直接显示写数据眼图的质量。读眼图扫描: 同样,可以扫描读数据眼图。信号完整性分析: 通过眼图,你可以清晰地看到信号是否张开,是否有过冲、下冲,最佳采样点在哪里。这为硬件整改提供了最直接的证据。

3. 软件配置检查

MIG配置: 再三确认输入的DDR3芯片时序参数是否正确?I/O标准、速度等级是否与硬件匹配?

引脚约束: 确保 .xdc 文件中的引脚位置和I/O标准100%正确。

四、 总结

DDR3的Training Process不是一项可选功能,而是其高速稳定运行的基石。它通过一套精密的自动化流程,动态地补偿了物理世界的不完美,将FPGA与DDR3颗粒“训练”成一个同步的、可靠的整体。

作为FPGA工程师,我们不仅要知其然(配置MIG)吉林炒股配资平台,更要知其所以然(理解训练)。当问题出现时,对训练过程的深刻理解,能让我们从“盲目试错”变为“有的放矢”,快速定位到问题的根源——无论是硬件设计缺陷、PCB制程问题,还是简单的配置错误。

辉煌优配吧提示:文章来自网络,不代表本站观点。